# Chapter 7

## Some aspects of the logical design of a control computer: a case study<sup>1</sup>

R. L. Alonso / H. Blair-Smith / A. L. Hopkins

*Summary* Some logical aspects of a digital computer for a space vehicle are described, and the evolution of its logical design is traced. The intended application and the characteristics of the computer's ancestry form a framework for the design, which is filled in by accumulation of the many decisions made by its designers. This paper deals with the choice of word length, number system. instruction set, memory addressing, and problems of multiple precision arithmetic.

The computer is a parallel, single address machine with more than 10,000 words of **16** bits. Such a short word length yields advantages of efficient storage and speed, but at a cost of logical complexity in connection with addressing. instruction selection, and multiple-precision arithmetic.

## 1. Introduction

In this paper we attempt to record the reasoning that led us to certain choices in the logical design of the **Apollo** Guidance Computer (AGC). The **AGC** is an onboard computer **for** one of the forthcoming manned space projects, a fact which is relevant primarily because it puts a high premium on economy and modularity of equipment, and results in much specialized input and output circuitry. The AGC, however, was designed in the tradition of parallel, single-address general-purpose computers, and thus has many properties familiar to computer designers [Richards, 1955], [Beckman et al., 1961]. We will describe some of the problems of designing a short word length computer, and the way in which the word length influenced some of its characteristics. These characteristics are number system, addressing system, order code, and multiple precision arithmetic.

A secondary purpose for this paper is to indicate the role of evolution in the AGC's design. Several smaller computers with about the same structure had been designed previously. One of these, MOD 3C, was to have been the Apollo Guidance Computer, but a decision to change the means of electrical implementation (from core-transistors to integrated circuits) afforded the **logical** designers an unusual second chance.

It is our belief, as practitioners of logical design, that designers, computers and their applications evolve in time: that a frequent <sup>1</sup>*IEEE Trans. EC-12* (6), 657-697 (December, 1963)

reason for  $\mathbf{a}$  given choice is that it is the same as, or the logical nest step to, a choice that was made once before.

A recent conference on airborne computers [Proc. Conf. Spaceborne Computer Eng., Anaheim, Calif., Oct. 30-31, 1962] affords a view of how other designers treated two specific problems: word length and number system. All of these computers have word lengths of the order of 22 to 28 bits, and use a two's complement system. The AGC stands in contrast in these two respects, and our reasons for choosing as we did may therefore be of interest as a minority view.

#### 2. Description of the AGC

The AGC has three principal sections. The first is a memory, the fixed (read only) portion of which has 24,376 words, and the erasable portion of which has 1024 words. The next section may be called the *central section;* it includes, besides an adder and a parity computing register, an instruction decoder (SQ), a memory address decoder (S), and a number of addressable registers with either special features or special use. The third section is the *sequence generator* which includes a portion for generating various microprograms and a portion for processing various interrupting requests.

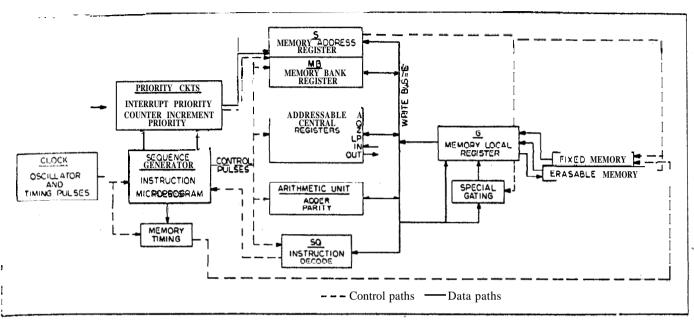

The backbone of the AGC is the set of 16 write busses: these are the means for transferring information between the various registers shown in Fig. 1. The arrowheads to and from the various registers show the possible directions of information flow.

In Fig. 1, the data paths are shown as solid lines: the control paths are shown as broken lines.

#### Memory: fixed and crasable

The Fixed Memory is made of wired-in "ropes" [Alonso and Laning, 1960], which are compact and reliable devices. The number of bits so wired is about  $4 \times 10^5$ . The cycle time is 12 µsec.

The erasable memory is a coincident current system with the same cycle time as the fixed memory. Instructions can address registers in either memory, and can be stored in either memory.

Chapter 7 | Some aspects of the logical design of a control computer: a case study 147

fig. 1. AGC block diagram.

The only logical difference between the two memories is the inability to change the contents of the fixed part by program steps.

Each word in memory is 16 bits long (15 data bits and an odd parity bit). Data words are stored as signed 14 bit words using a one's complement convention. Instruction words consist of 3 order code bits and 12 address code bits.

The contents of the address register S uniquely determine the address of the memory word only if the address lies between octal 0000 and octal 5777, inclusive. If the address lies between octal 6000 and octal 7777, inclusive, the address in S is modified by the contents of the memory bank register MB. The modification consists in adding some integral multiplies of octal 2000 to the address in S before it is interpreted by the decoding circuitry. The memory bank register MB is itself addressable; its address, however, is not modified by its own contents.

Transfers in and out of memory are made by way of a memory local register G. For certain specific addresses, the word being transferred into G is not sent directly, but is modified by a special gating network. The transformations on the word sent to G are right shift, left shift, right cycle, and left cycle.

#### Central section

The middle part of Fig. 1 shows the central section in block form. It consists of the address register S and the memory bank register

*ME* both of which were mentioned above. There is also a block of addressable registers called "central and special registers," which will be discussed later, an arithmetic unit, and an instruction decoder register SQ.

The arithmetic unit has a parity generating register and an adder. These two registers are not explicitly addressable.

The SQ register bears the same relation to instructions as the S register bears to memory locations; neither S nor SQ are explicitly addressable.

The central and special registers are A, Q, Z, *LP*, and a set of input and output registers. Their properties are shown in Table 1.

#### Sequence generator

The sequence generator provides the basic memory timing, the sequences of control pulses (microprograms) which constitute an instruction, the priority interrupt circuitry, and a number of scaling networks which provide various pulse frequencies used by the computer and the rest of the navigation system.

Instructions are arranged so as to last an integral number of memory cycles. The list of 11 instructions *is* treated in detail in Sec. 6. In addition to these there are a number of "involuntary" sequences, not under normal program control, which may break into the normal sequence of instructions; these are triggered either by external events, or by certain overflows within the AGC, and 148 Part 2 The instruction-set processor: main-line computers

| Register(s) | Octal<br>address | Purpose and or properties                                                                                                                 |

|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| A           | 0000             | Central accumulator. Most instructions refer<br>to A.                                                                                     |

| Q           | 0001             | If a transfer of control (TC) occurred at $L$ ,<br>(Q) = $L + 1$ .                                                                        |

| Z           | 0002             | Program counter. Contains $L + 1$ , where $L$ is the address of the instruction presently being executed.                                 |

| I. <b>P</b> | 0003             | Low product register. This register modifie<br>words written into it by shifting them in a<br>special way.                                |

| IN          |                  | Several registers which arc used for sampling<br>either external lines. or internal computer<br>conditions <b>such as</b> time or alarms. |

| OUT         |                  | Several output registers whose bits contro<br>switches, networks, and displays.                                                           |

may be divided into two categories: counter incrementing and program interruption.

Counter incrementing may take place between any two memory cycles. External requests for incrementing a counter are stored in a counter priority circuit. At the end of every memory cycle a test is made to see if any incrementing requests exist. If not, the nest normal memory cycle is esecuted directly, with no time between cycles. If a request is present, an incrementing memory cycle is executed. Each "counter" is a specific location in erasable memory. The incrementing cycle consists of reading out the word stored in the counter register, incrementing it (positively or negatively), or shifting it, and storing the results back in the register of origin. All outstanding counter incrementing requests are processed before proceeding to the nest normal memory cycle. This type of interrupt provides for asynchronous incremental or serial entry of information into the working erasable memory. The program steps may refer directly to a "counter" to obtain the desired information and do not have to refer to input buffers. Overflows from one counter may be used as the input to another. A further property of this system is that the time available for normal program steps is reduced linearly by the amount of counter activity present at any given time.

Program interruption occurs between normal program steps

rather than between memory cycles. An interruption consists o storing the contents of the program **counter** and transferring control to a fixed location. Each interrupt line has a different locatior associated with it. Interrupting programs may not be interrupted but interrupt requests are not lost, and are processed as soon a the earlier interrupted program is resumed. Culling the resumsequence, which restores the program counter, is initiated by referencing a special address.

## 3. Word length

In an airborne computer, granted the initial choice of parallel transfer of words within it, it is highly desirable to minimize the word length. This is because memory sense amplifiers, being high-gain class A amplifiers, are considerably harder to operate with wide margins (of temperature, voltages, input signal) than, say, the circuits made up of NOR gates. It is best to have as few of these as possible. Furthermore, the number of ferrite-plane inhibit drivers equals the number of bits in a word in this case. Similarly, the time required for a carry to propagate in a parallel adder is proportional to the word length, and in the present case, this factor could be expected to affect the microprogram-ning of instructions. The initial intent, then, was to have **as** short a word length as possible.

Another initial choice is that the AGC should be a "common storage" machine, which means that instructions may be executed from erasable memory as well as **from fixed memory**, and that **data** (obviously constants, in the case of fixed memory) may be stored in either memory. This in turn means that the word sizes of both types of memory must be compatible **in** some sense;, for the AGC, the easiest form of compatibility is to have equal word lengths. So-called "separate storage" solutions which allow different word lengths for instructions and data can **be made** to work [Walendziewicz, 1962] but they have a drawback in that three memories are then required: a data memory (erasable), and two fised memories, one for instructions and one for constants. In addition, we have found that separate storage machines are more awkward to program, and use memory less efficiently. than common storage machines.

There are three principal factors in the choice of word length. These are:

- 1 Precision desired in the representation of navigational variables.

- 2 Range of the input variables which are entered serially and counted.

3 Instruction word format. Division of instruction words into two fields, one for operation code and one for address.

As a start, the choice of word length (15 bits) for two previous machines in this series was kept in mind as a satisfactory word length from the point of view of mechanization; *i.e.*, the number of sense amplifiers, inhibit drivers, the carry propagation time, etc., were all considered satisfactory. The act of "choosing" word length really meant whether or not to alter the word length, at the time of change from MOD 3C to the AGC, and in particular whether to increase it. The influence of the three principal factors will be taken up in turn.

## Precision of data words

The data words used in the AGC may be divided roughly into two classes: data words used in elaborate navigational computations, and data words used in the control of various appliances in the system. Initial estimates of the precision required by the first class ranged from 27 to 32 bits,  $O(10^{8\pm1})$ . The second class of variables could almost always be represented with 15 bits. The fact that navigational variables require about twice the desired 15-bit word length means that there is not much advantage to word sizes between 15 and 28 bits, as far as precision of representation of variables is concerned, because double-precision numbers must be used in any event. Because of the doubly signed number representation for double-precision words, the equivalent word length is 29 bits (including sign), rather than 30, for a basic word length of 15 bits.

The initial estimates for the proportion of 15-bit vs 29-bit quantities to be stored in both fixed and erasable memories indicated the overwhelming preponderance of the former. It was also estimated that a significant portion of the computing had to do with control, telemetry and display activities, all of which can be handled more economically with short words. A short word length allows faster and more efficient use of erasable storage because it reduces fractional word operations, such as packing and editing; it also means a more efficient encoding of small integers.

#### Range of input variables

As a control computer, the AGC must make analog-to-digital conversions, many of which are of shaft angles. Two principal forms of conversion exist: one renders a whole number, the other produces a train of pulses which must be counted to yield the desired number. The latter type of conversion is employed by the AGC, using the counter incrementing feature.

When the number of bits of precision required is greater than the computer's word length, the effective length of the counter must be extended into a second register, either by programmed scanning of the counter register, or by using a second counter register to receive the overflows of the first. Whether programmed scanning is feasible depends largely on how frequently this scanning must be done. The cost of using an extra counter register is directly measured in terms of the priority circuit associated with it.

In the AGC, the equipment saved by reducing the word length below 15 bits would probably not match the additional expense incurred in double-precision extension of many input variables. The question is academic, however, since a lower bound on the word length is effectively placed by the format of the instruction word.

## Instruction word format

An initial decision was made that instructions would consist of an operation code and a single address. The straightforward choices of packing one or two such instructions per word were the only ones seriously considered, although other schemes, such as packing one and a half instructions per word, are possible [England, 19621. The previous computers MOD 3S and MOD 3C had a 3-bit field for operation codes and a 12-bit field for addresses, to accommodate their 8 instruction order codes and 4096 words of memory. In the initial core-transistor version of the AGC (i.e., MOD 3C), the 8 instruction order codes were in reality augmented by the various special registers provided, such as shift right, cycle left, edit, so that a transfer in and out of one of these registers would accomplish actions normally specified by the order code (see Sec. 6). These registers were considered to be more economical than the corresponding instruction decoding and control pulse sequence generation. Hence the 3 bits assigned to the order code were considered adequate, albeit not generous. Furthermore, as will be seen, it is possible to use an indexing instruction so as to increase to eleven the number of explicit order codes provided for.

The address field of 12 bits presented a different problem. At the time of the design of MOD 3C we estimated that 4000 words would satisfy the storage requirements. By the time of redesign it was clear that the requirement was for  $10^5$  words, or more, and the question then became whether the proposed estension of the address field by a bank register (*see*Sec. 7) was more economical than the addition of 2 bits to the word length. For reasons of modularity of equipment, adding 2 more bits to the word length would result in adding 2 more bits to all the central and special registers, which amounts to increasing the size of the nonmemory portion of the AGC by 10 per cent.

Chapter 7 Some aspects of the logical design of a control computer: a case study 149

150 Part 2 The instruction-set processor: main-line computers

In summary, the 15-bit word length seemed practical enough so that the additional cost of extra bits in terms of size, weight, and reliability did not seem warranted. A 14-bit word length was thought impractical because of the problems with certain input variables, and it would further restrict the already somewhat cramped instruction word format. Word lengths of 17 or 18 bits would result in certain conceptual simplicities in the decoding of instructions and addresses, but would not help in the representation of navigational variables. These require 28 bits, and so they must be represented to double precision in any event.

#### 4. Number representation

#### Signed numbers

In the absence of the need to represent numbers of both signs, the discussion of number representation would not extend beyond the fact that numbers in AGC are expressed to base two. But the accommodation of both positive and negative numbers requires that the logical designer choose among at least three possible forms of binary arithmetic. These three principal alternatives are: (1) one's complement, (2) two's complement, and (3) sign and magnitude [Richards. 1955].

In one's complement arithmetic, the sign of a number is reversed by complementing every digit, and "end around carry" is required in addition of two numbers.

In two's complement arithmetic, sign reversal is effected by complementing each bit and adding a low order **one**, or some equivalent operation.

Sign and magnitude representation is typically used where direct human interrogation of memory is desired, as in "postmortem" memory dumps. for example, The addition of numbers of opposite sign requires either one's or two's complementation or comparison of magnitude, and sometimes may use both. No advantage is offered in efficiency with the possible exception of sign changing, which only requires changing the sign bit. A disadvantage is engendered in magnetic core logic machines by the extra equipment needed for subtraction or conditional recomplementation.

The one's complement notation has the advantage of having easy sign reversal, which is equivalent to Boolean complementation: hence a single machine instruction performs both functions. Zero is ambiguously represented by all zero's and by all ow's, so that the number of numerical states in an *n*-bit word is  $2^n - 1$ .

Two's complement arithmetic is advantageous where end around carry is difficult to mechanize, as is particularly true in serial computers. An *n*-bit word has  $2^n$  states, which is desirable for input conversions from such devices **as** pattern generators, geared encoders, or binary scalers. Sign reversal is awl-ward, however, since **a** full addition is required in the process.

The choice in the case of the AGC was to use one's complement arithmetic in general processing. and two's complements for certain input angle conversions. Since the only arithmetic done in the latter case is the addition of plus or minus *one*, the two's complement facility is provided simply by suppressing end around carry and using the proper representation of minus **one**. The latter is stored **as** a fixed constant. so that no sign reversal is required.

#### Modified one's complement system

In a standard one's complement adder, overflow is detected by examining carries into and out of the sign position These overflow indications must be "caught on the fly" and stored separately if they are to be acted upon later. The number system adopted in the ACC has the advantage of being a one's complement system with the additional feature of having a static indication of overflow. The implementation of the method depends on 'the AGC's not using a parity bit in most central registers. Because of certain modular advantages, 16, rather than 15, columns are available in all of the central registers, including the adder. Where the parity bit is not required, the extra bit position is used as an extra column. The virtue of the 16-bit adder is that the overflow of **a** 15-bit sum is readily detectable upon examination of the two high order bits of the sum (see Fig. 2). If both of these bits are the same, there is no overflow. If they are different, overflow has occurred with the sign of the highest order bit.

The interface between the 16-bit adder and the 15-bit memory is arranged so that the sign bit of a word coming from memory enters both of the two high order adder columns. These are denoted  $S_2$  and  $S_1$  since they both have the significance of sign bits. When a word is transferred from the accumulator A to memory, only one of these two signs can be stored. Our choice was to store the  $S_2$  bit, which is the standard one's complement sign except in the event of overflow, in which case it is the sign of the two operands. This preservation of sign on overflow is an important asset in dealing with carries between component words of multiple-precision numbers (see Sec. 5).

In a standard one's complement system, a series of additions may result in subtotals which overflow, yet still produce a valid sum solong as the total does not exceed the capacity of one word. In a modified one's complement system, however, where sign is preserved on overflow, this is no longer true; and the total may depend on the order in which the numbers are added; this is not a serious drawback, but it must be accounted for in all phases of logical design and programming. Chapter 7 | Some aspects of the logical design of a control computer: a case study 151

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | STANDARD          |               |   |   | MODIFIED         |      |                |                |          |     |   |                     |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|---|---|------------------|------|----------------|----------------|----------|-----|---|---------------------|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S <sub>1</sub>    | 4             | 3 | 2 | 1                |      | S <sub>2</sub> | S <sub>1</sub> | 4        | 3   | 2 | 1                   |

| EXAMPLE 1:        | Both operands positive; Sum positive, no overflow. Identical results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                 | 0             | 0 | 0 | 1                |      | 0              | 0              | 0        | 0   | 0 | 1                   |

|                   | in both systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |               | 0 | 1 | 1                |      | 0              | 0              | 0        | 0   | 1 | 1                   |

|                   | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | 0             | 1 | 0 | 0                |      | 0              | 0              | 0        | 1   | 0 | 0                   |

| EXAMPLE 3:        | Both operands positive; positive overflow. Standard result is negative; Modified result is positive using $S_2$ as sign of the answer.<br>Positive overflow indicated by $S_1 \cdot \overline{S}_2$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                 | 1             | 0 | 0 | 1                |      | 0              | 0              | 1        | 0   | 0 | 1                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                 | 1             | 0 | 1 | 1                |      | 0              | 0              | 1        | 0   | 1 | 1                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                 | 0             | 1 | 0 | 0                |      | 0              | 1              | 0        | 1   | 0 | 0                   |

| EXAMPLE 3.        | Both operands negative; Sum negative, no overflow. End around carry occurs. Identical results in both systems using either $S_1$ or $S_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   | 1             | 1 | 1 | 0                |      | 1              | 1              | 1        | 1   | 1 | 0                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | 1             | 1 | 0 | 0                |      | 1              | 1              | 1        | 1   | 0 | 0                   |

|                   | as the sign of the answer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                 | 1             | 0 | 1 | 0                |      | 1              | 1              | 1        | 0   | 1 | 0                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | 1             | 0 | 1 | $\frac{1}{1}$ ca | arry |                | 1              | 1        | 0   | 1 | $\frac{1}{1}$ carry |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                 | 1             | 0 |   |                  |      |                | 1              |          |     |   | 1                   |

| EXAMPLE <b>4:</b> | Both operands negative; negative overflow. Standard result is <b>posi</b> tive: modified result is negative using $S_2$ as the sign <i>of</i> the answer.<br>Negative overflow indicated by $\overline{S}_1 \cdot S_2$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                 | 0             | 1 | 1 | 0                |      | 1              | 1              | 0        | 1   | 1 | 0                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                 | 0             | 1 | 0 | 0                |      | 1              | 1              | 0        | 1   | 0 | 0                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                 | 1             | 0 | 1 | 0                |      | 1              | 0              | 1        | 0   | 1 | 0                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\overline{0}$    | 1             | 0 | 1 | $\frac{1}{1}$ ca | arry | 1              | 0              | 1        | 0   | 1 | $\frac{1}{1}$ carry |

|                   | Or and have a second size of the size of t |                   |               | 1 | 1 |                  |      |                |                |          | 1   | 1 |                     |

| EXAMPLE 5:        | Operands have opposite sign; Sum positive. Identical results in <b>both</b> systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                 | $\frac{1}{0}$ | 0 | 1 | 1                |      | 1              | 1              | $1 \\ 0$ | 1   | 1 | 1                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{\circ}{0}$ | 0             | 0 | 0 | 1                |      | $\frac{0}{0}$  | 0              | 0        | 0   | 0 | 1                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ũ                 | Ũ             | Ũ | Ŭ | 1 ca             | arry | Ũ              | Ŭ              | Ű        | Ũ   | 0 | 1 carr              |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                 | 0             | 0 | 1 | 0                |      | 0              | 0              | 0        | 0   | 1 | 0                   |

| EXAMPLE 6:        | Operands have opposite sign: sum negative. Identical results in both systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                 | 1             | 1 | 0 | 0                | -    | 1              | 1              | 1        | 1   | 0 | 0                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                 | 0             | 0 | 0 | 1                |      | 0              | 0              | 0        | 0   | 0 | 1                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                 | 1             | 1 | 0 | 1                |      | 1              | 1              | 1        | ' 1 | 0 | 1                   |

Fig. 2. Illustrative example of properties of modified one's complement system.

## 5. Multiple precision arithmetic